# Towards lowering the overhead of Open-Channel SSD

Freysteinn Alfreðsson

Thesis of 60 ECTS credits

Master of Science (M.Sc.) in Computer Science

January 2019

# Towards lowering the overhead of Open-Channel SSD

by

## Freysteinn Alfreðsson

Thesis of 60 ECTS credits submitted to the School of Computer Science at Reykjavík University in partial fulfillment of the requirements for the degree of Master of Science (M.Sc.) in Computer Science

January 2019

#### Supervisors:

Dr. Gylfi Þór Guðmundsson, Supervisor Adjunct Professor, Reykjavík University, Iceland

Dr. Philippe Bonnet, Co-Supervisor Full Professor, IT University, Denmark

#### Committee Members:

Dr. Björn Þór Jónsson, Committee Member Associate Professor, ITU, Denmark

Dr. Marcel Kyas, Committee Member Assistant Professor, Reykjavík University, Iceland Copyright

Freysteinn Alfreðsson

January 2019

# Towards lowering the overhead of Open-Channel SSD

Freysteinn Alfreðsson

January 2019

#### **Abstract**

The revolutionary change that Solid State Disks (SSDs) have introduced to the storage space industry has added many new challenges for data-driven application developers when developing execution planners. Traditionally the application, operating system, and storage controller have all separately handled the storage access pattern optimization and scheduling. Despite successful use for decades, due to the predictable behavior of the spinning disks, finding similar guidelines for optimizing access to SSDs has proven much harder. The problem is in part due to their increased performance but mostly due to their unpredictable behavior and black box nature. The key to addressing this issue is to open up the black-box, exposing the internal complexity of maintaining a healthy SSD, such that the schedulers can take the actual cost of all operations into account in their planning. The first contribution of this thesis is a user-space library called LightNVM-Direct that uses the Open-Channel SSD protocol to expose the internals of a compliant SSD device. The direct communication allows LightNVM-Direct to bypass the kernel entirely and eliminate all of its overhead. This bypass leaves the optimization and scheduling solely in the hands of the developer of the data-driven user-space application. We used the uFLIP-OC benchmark to evaluate LightNVM-Direct using an SSD device called Dragon Fire Card. The results were inconclusive, however, as little gain was observed in overall throughput despite the lower kernel overhead. The second contribution is a proposal of a new protocol we called RNVMe, that adds near-data processing capabilities by allowing part of the application to run on the SSD in the form of Remote Procedure Calls (RPC). This RPC mechanism would enable applications to run simple functions, such as filters and data pre-processing, before delivering the final result to the host computer.

# Umstangs lágmörkun á Open-Channel SSD

Freysteinn Alfreðsson

janúar 2019

#### Útdráttur

Solid State Diskar (SSD) hafa umbylt gagnageymsluiðnaðinum en hafa einnig kynnt til sögunar nýjar áskoranir fyrir forritara sem búa til aðgangsstýringar. Sögulega hafa forritin, stýrikerfið og diskarnir séð um að hámarka afköst gagnaaflesturs af diskum óháð hvert öðru. Síðustu áratugi hefur þetta fyrirkomulag fyrst og fremst gengið upp vegna þess hve reglubundin og fyrirsjáanleg hegðun hefðbundinna mekanískra diska er. Ekki hefur gengið jafn vel að finna sambærilega hlutverkaskiptingu fyrir nýju SSD diskana. Vandamálið er í raun bríþætt: Fyrst þurfti að uppfæra mikið af hugbúnaðinum þar sem að afkastageta diskanna varð fljótt mun meiri en nokkur hafði gert ráð fyrir; Mun alvarlegri vandi liggur hinsvegar í því að erfiðara er að spá fyrir um hegðun diskanna og einnig því að diskarnir eru í raun lokað kerfi sem enginn nema framleiðandinn veit nákvæmlega hvernig virkar. Þetta gerir það að verkum að aðgangsstýringarnar á efri lögum eiga erfitt með að spá fyrir um kostnað aðgerða og því er erfitt um vik að skipuleggja aðgangsstýringar. Open-Channel SSD er viðbót við NVMe staðalinn sem opnar á möguleika fyrir SSD framleiðendur að svipta hulunni af hegðun diska þeirra. Að opna á bein samskipti við diskana er ekki nóg til að leysa vandann því aðgangsstýringarnar á efri lögunum taka á sig bæði aukið flækjustig og aukna ábyrgð. Í þessari ritgerð eru lögð drög að því að lágmarka umstangið og kostnaðinn við að útfæra aðgangsstýringu í notendaforriti. Fyrsta framlag okkar er að klippa út stýrikerfið (kjarnann) með því að útfæra og prófa forritasafn sem við köllum LightNVM-Direct. Með beinum samskiptum milli notendaforrits og SSD disks getur LightNVM-Direct farið framhjá stýrikerfiskjarnanum og losað þannig við allan kostnað og umstang sem því fylgir. Þetta fyrirkomulag færir aðgangsstýringuna alfarið í hendur notendaforritsins, án afskipti hinna lagana. Við notuðum uFLIP-OC til að bera saman frammistöðu LightNVM-Direct og hefðbundari útfærslu sem kallast LightNVM. Seinna framlag ritgerðarinnar er tillaga að nýjum samskiptastaðli sem við köllum RNVMe, sem veitir örgagnavinnslu eiginleika á gagnageymslunni. Þetta er gert með því að leyfa hluta af forritinu að keyra á SSD gagnageymslunni sem Remote Procedure Call (RPC). Þetta gerir forritum kleift að kalla á einfaldar aðgerðir sem geta síað og forunnið gögnin áður en þeim er skilað til tölvunnar.

# Towards lowering the overhead of Open-Channel SSD

Freysteinn Alfreðsson

Thesis of 60 ECTS credits submitted to the School of Computer Science at Reykjavík University in partial fulfillment of the requirements for the degree of

Master of Science (M.Sc.) in Computer Science

|                    | January 2019              |  |  |

|--------------------|---------------------------|--|--|

| Student:           | Freysteinn Alfreðsson     |  |  |

| Supervisors:       | Dr. Gylfi Þór Guðmundsson |  |  |

|                    | Dr. Philippe Bonnet       |  |  |

| Committee Members: | Dr. Björn Þór Jónsson     |  |  |

|                    | Dr. Marcel Kyas           |  |  |

The undersigned hereby grants permission to the Reykjavík University Library to reproduce single copies of this Thesis entitled **Towards lowering the overhead of Open-Channel SSD** and to lend or sell such copies for private, scholarly or scientific research purposes only. The author reserves all other publication and other rights in association with the copyright in the Thesis, and except as herein before provided, neither the Thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatsoever without the author's prior written permission.

| date                  |      |  |

|-----------------------|------|--|

|                       |      |  |

|                       | <br> |  |

| Freysteinn Alfreðsson |      |  |

| Master of Science     |      |  |

# **Contents**

| Co | onten   | ts            |                                                | xi   |

|----|---------|---------------|------------------------------------------------|------|

| Li | st of l | Figures       |                                                | xiii |

| Li | st of ' | <b>Fables</b> |                                                | xv   |

| Li | st of A | Abbrevi       | iations                                        | xvii |

| 1  | Intr    | oductio       | on                                             | 1    |

| 2  | Bac     | kgroun        | d                                              | 3    |

|    | 2.1     | Non-V         | Volatile Memory Express (NVMe)                 | 3    |

|    |         | 2.1.1         | DMA memory                                     | 4    |

|    |         | 2.1.2         | NVMe queues                                    | 4    |

|    |         | 2.1.3         | The queue structure and notification doorbells | 5    |

|    |         | 2.1.4         | NVMe commands                                  | 6    |

|    | 2.2     | User-S        | Space NVMe                                     | 6    |

|    |         | 2.2.1         | Requirements                                   | 7    |

|    |         | 2.2.2         | Available user-space NVMe libraries            | 10   |

|    |         | 2.2.3         | The NVMeDirect framework                       | 11   |

|    |         | 2.2.4         | Drawbacks of the Kernel bypass                 | 12   |

|    | 2.3     | Solid S       | State Disk (SSD)                               | 13   |

|    |         | 2.3.1         | Flash Translation Layer (FTL)                  | 14   |

|    |         | 2.3.2         | Open-Channel SSD                               | 15   |

|    |         | 2.3.3         | liblightnvm                                    | 15   |

|    |         | 2.3.4         | Dragon Fire Card                               | 16   |

|    |         | 2.3.5         | OX Controller                                  | 17   |

|    | 2.4     | Bench         | ımarking                                       | 19   |

|    |         | 2.4.1         | uFLIP                                          | 19   |

|    |         | 2.4.2         | uFLIP-OC / Fox                                 | 19   |

| 3  | Deb     | ugging        | Framework                                      | 21   |

|    | 3.1     | OX ru         | n-time command line                            | 21   |

|    | 3.2     | Discus        | ssion                                          | 24   |

|    | -       | 3.2.1         | Future Work                                    | 24   |

| 4  | Ligh    | ntNVM         | -Direct: A liblightnym Kernel Bypass           | 27   |

|    | 4.1     | Archit        | tecture                                        | 27   |

|    |         | 4.1.1         | Changes to liblightnym                         | 27   |

|    |         | 112           | Changes to NVMeDirect                          | 28   |

| Bi | bliogr | aphy           |                                                  | 55             |

|----|--------|----------------|--------------------------------------------------|----------------|

| 6  | Con    | clusion        |                                                  | 53             |

|    |        | 5.6.1          | Future Work                                      | 51             |

|    | 5.6    | Discus         | sion                                             | 51             |

|    |        | 5.5.2          | Preventing malicious uploads of AppNVM           | 50             |

|    |        | 5.5.1          | Preventing malicious DMA transfers from the host | 50             |

|    | 5·5    |                | ty                                               | 50             |

|    | 5.4    |                | ppNVM Upload Protocol                            | 48             |

|    |        | 5.3.2          | The OX RNVMe Modular Backend                     | 47             |

|    | 5.5    | 5.3.1          | The OX RNVMe Command Handler                     | 45             |

|    | 5.3    | U              | VVMe Architecture                                | 45<br>45       |

|    | ر. 2   | 5.2.1          | The RNVMe command                                | 43             |

|    | 5.2    |                | Ie: Our proposal for a NVMe RPC protocol         | 42             |

|    |        | 5.1.4          | Full AppNVM                                      | 41             |

|    |        | 5.1.3<br>5.1.4 | NVMe Inter-Process Communication (NVMe IPC)      | 41<br>41       |

|    |        | 5.1.2          | Thin-AppNVM                                      | 40             |

|    |        | 5.1.1          | NVMe Rule Engine (NVMe RE)                       | 40             |

|    | 5.1    |                | ion and Categorization of AppNVM                 | 40             |

| 5  |        | NVM            | ing and Catananiastica of Ann NIVIM              | 39             |

|    |        | 4.3.2          | Future Work                                      | 36             |

|    |        | 4.3.1          | Sources of Complexity                            | 36             |

|    | 4.3    | Discus         | sion                                             | 35             |

|    |        | 4.2.6          | Evaluation 5: Latency                            | 34             |

|    |        | 4.2.5          | Evaluation 4: Thread Throughput                  | 32             |

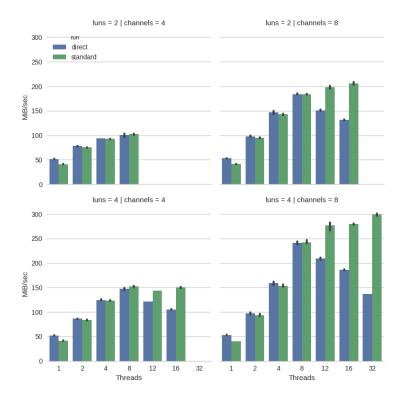

|    |        | 4.2.4          | Evaluation 3: Write Throughput                   | 32             |

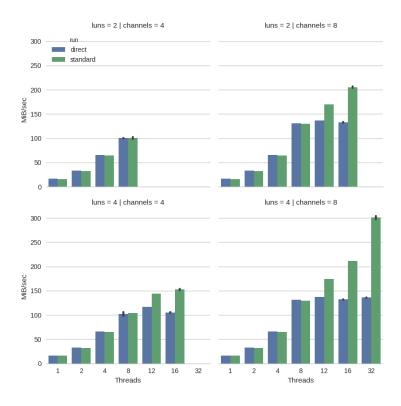

|    |        | 4.2.3          | Evaluation 2: Read Throughput                    | 31             |

|    |        | 4.2.2          | Evaluation 1: Context-switching                  | 30             |

|    |        | 4.2.1          | Experimental Setup                               | <del>-</del> 9 |

|    | 4.2    |                | ments with LightNVM-Direct                       | 29<br>29       |

|    |        | 4.1.4          | Data Path                                        | 29<br>29       |

|    |        | 4.1.3          | Control Path                                     | 29             |

# **List of Figures**

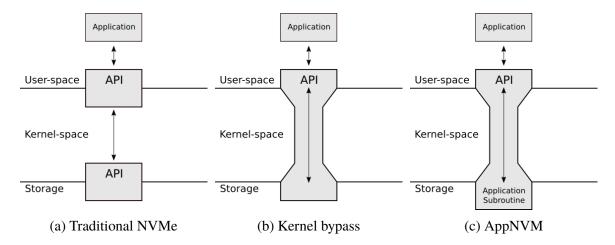

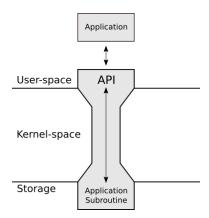

| 1.1 | Overview of the communication pathway of the I/O traffic from user-space applications down to the storage device(s). In figure (a) we see the standard I/O traffic passing through the operating system's API. In (b) we see how the Kernel can be bypassed to reduce overhead. Finally, in (c) we depict how we can delegate part of the application logic to the storage device for near data processing.      | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

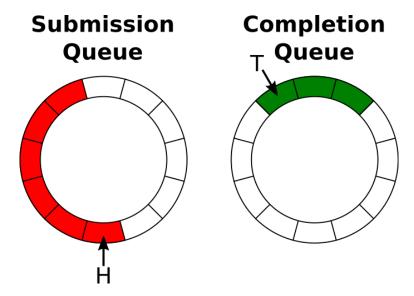

| 2.1 | NVMe queues are DMA buffers used by the host to submit commands to the NVMe device. The queues are circular buffers, where the submission queue is used by the host to submit commands, and the completion queue is used to notify the host of completed commands. The host keeps track of the tail pointer of the submission queue, and the NVMe device keeps track of the head pointer of the completion queue | 5  |

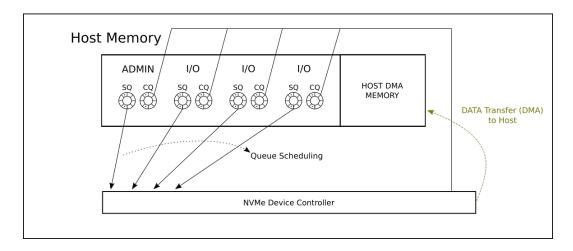

| 2.2 | NVMe devices have one admin queue which the host uses to create submission and completion queues. The queues are DMA memory buffers which the host uses to send I/O commands to the NVMe device. This Figure is based on a Figure by Picoli [5]                                                                                                                                                                  | 5  |

| 2.3 | The NVMe command entries written to the submission queue by the host are 64-bytes, or 16 double words (DWORDs), where all NVMe commands have the same format for the first two DWORDs. However, the opcode decides the format of the rest of the DWORDs                                                                                                                                                          | 8  |

| 2.4 | NVMe completion entries are written by NVMe device to the completion queue. These entries are 32-bytes where all DWORDs follow the same standard format.                                                                                                                                                                                                                                                         | 8  |

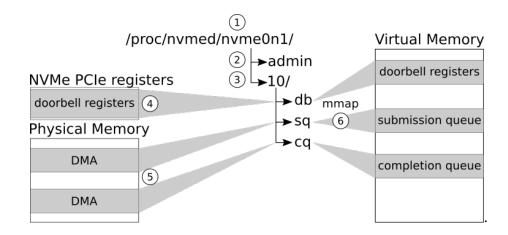

| 2.5 | NVMeDirect <i>proc</i> file-system hierarchy is used by the user-space application to create new NVMe queues and to map them into its virtual memory address space using <i>ioctl</i> function calls                                                                                                                                                                                                             | 11 |

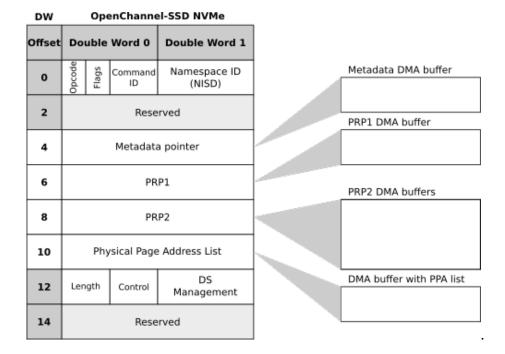

| 2.6 | Open-Channel SSD NVMe Command structure has the same structure for read, write, and erase commands. The PRP entries are pointers to either data to be read or written to the NVMe device depending on the type command submitted. The PPA list contains the list of NVMe physical addresses which the command is going to operate.                                                                               | 16 |

| 2.7 | All of our work and experiments were conducted on the Dragon Fire Card                                                                                                                                                                                                                                                                                                                                           | 17 |

| 2.8 | This Figure shows the internals of the OX controller as depicted by Picoli [5]. The OX Controller is the first open source Open-Channel SSD firmware controller. OX supports multiple types of FTLs implementations and different types of                                                                                                                                                                       | ,  |

|     | media managers for different types of storage technologies                                                                                                                                                                                                                                                                                                                                                       | 18 |

| 3.1 | OX command line showing the help system                                                                                                                                                                                                                                                                                                                                                                          | 23 |

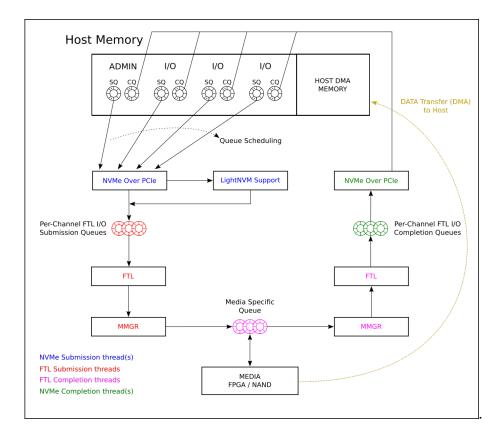

| 4.1        | We separated the control and data paths in our implementation of NVMeDirect.           |    |

|------------|----------------------------------------------------------------------------------------|----|

|            | This separation enabled us to use the <i>nvme</i> driver for admin commands and to     |    |

|            | use a kernel bypass for I/O commands                                                   | 28 |

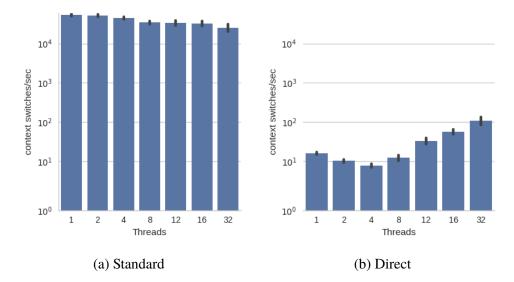

| 4.2        | Both figures show context switches through all the experiments in logarithmic          |    |

|            | scale, where (a) is the context switches using the standard <i>liblightnvm</i> and (b) |    |

|            | uses our kernel bypass, LightNVM-Direct                                                | 30 |

| 4.3        | The bar charts show combined experiments using 100% read throughput of                 |    |

|            | pattern engines 1, 2, and 3, for both Standard and Direct experiments                  | 32 |

| 4.4        | The bar charts show write throughput using pattern engine 1 using 100% write           |    |

|            | operations                                                                             | 33 |

| 4.5        | The bar charts show combined experiments using 100% write throughput using             |    |

|            | pattern engines 2 and 3                                                                | 33 |

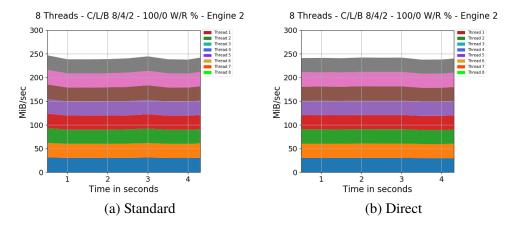

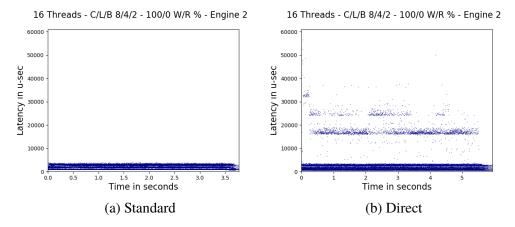

| 4.6        | The area chart shows the throughput of 8 threads during 100% write using pattern       |    |

|            | engine 2 with and without a kernel bypass                                              | 34 |

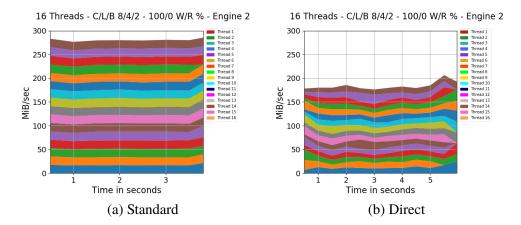

| 4.7        | The area chart shows the throughput of 16 threads during 100% write using              |    |

|            | pattern engine 2 with and without a kernel bypass. The chart is more erratic in        |    |

|            | (b) because the thread count is higher than the number of CPU cores                    | 34 |

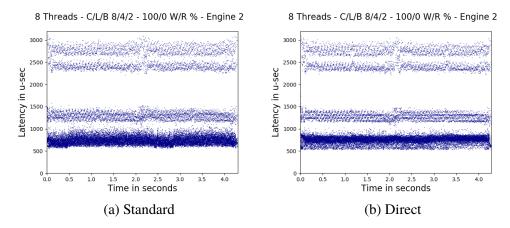

| 4.8        | The scatter plot shows the latency of writes during experiments using pattern          |    |

|            | engine 2 running with eight threads                                                    | 35 |

| 4.9        | The scatter plot shows the latency of writes during experiments using pattern          |    |

|            | engine 2 running with sixteen threads. Writes in (b) show multiple outliers that       |    |

|            | have up to an order of magnitude worse latency than in (a)                             | 35 |

| 5.1        | RNVMe is an NVMe RPC protocol that allows the application programmer to                |    |

| J.1        | call subroutines that are capable of NDP on the NVMe device. By moving part            |    |

|            | of the application specific functionality onto the NVMe device, we are not only        |    |

|            | bypassing the kernel but the overhead of the PCIe layer as well                        | 39 |

| 5.2        | The proposed RNVMe command identifies the RPC function using the combined              | 3) |

| <i>J</i> . | values of the vendor and the function fields. The rest of the fields are used for      |    |

|            | parameters to the function and return values. The parameters and return values         |    |

|            | can either be a 64-bit value or a pointer to a DMA buffer                              | 45 |

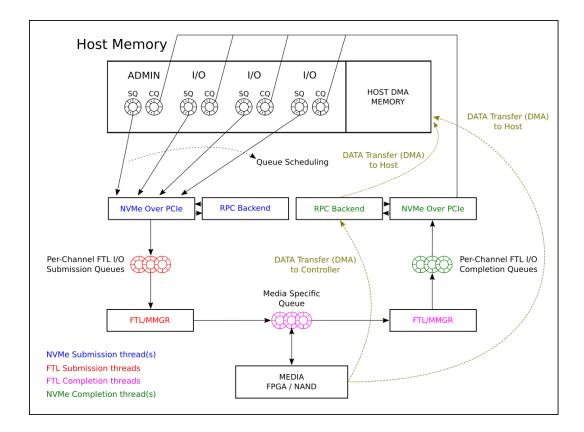

| 5.3        | This Figure shows the internals of the OX controller as depicted by Picoli [5]. It     |    |

|            | has been modified to show the design change needed to OX to add a new RPC              |    |

|            | backend that is capable of submitting multiple I/O requests to the internal queues     |    |

|            | which are not visible to the host. Each RPC command can result in this backend         |    |

|            | submitting and completing multiple commands to complete an RPC NVMe and                |    |

|            | sending a completion entry back to the host                                            | 46 |

# **List of Tables**

| 2.1 | This table lists the most common NVMe admin commands. It is only possible                                                                                                                                                                                                                                                          |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | to send these commands to the admin queue                                                                                                                                                                                                                                                                                          | 6        |

| 2.2 | The NVMe BAR is the main interface for interacting with the NVMe device. The ASQ and ACQ are used to map the Admin submission and completion queues to DMA buffers, and the doorbell registers from addresses 1000h and upwards are used to notify the NVMe device of new NVMe commands and handled completed commands by the host | 7        |

| 2.3 | This table lists the most common NVMe commands. It is only possible to submit these commands to I/O submission and completion queues                                                                                                                                                                                               | 8        |

| 2.4 | The user-space application uses these NVMeDirect <i>ioctl</i> attributes when it interacts with the <i>/proc/nvmed/nvmeon1/admin</i> file                                                                                                                                                                                          | 12       |

| 2.5 | Whenever the user-space application creates a new queue using the NVMeDirect kernel module, it creates a directory in the <i>proc</i> file-system with the queues identification number using the sq, cq, and db files. These files are then used by the user-space application to map the PCIe registers and submission and       |          |

| 2.6 | completion queue DMA buffers into the applications virtual address space New <i>liblightnvm</i> backends need to implement the interface listed in this table. It is the core interface used by the <i>liblightnvm</i> framework to interact with its backends and therefore the NVMe device                                       | 12       |

| 3.1 | The table lists the commands in the main category of the debugging command line                                                                                                                                                                                                                                                    | 22       |

| 4.1 | The table lists all parameters and values related to our experiments that we ran with Fox. We skipped all the combinations where the threads were less than channels multiplied by LUNs. These settings resulted in 270 different                                                                                                  |          |

| 4.2 | experiments in total                                                                                                                                                                                                                                                                                                               | 29<br>29 |

| 4.3 | The table shows the latency statistics for the experiments in Figures 4.8 and 4.9. The experiments used pattern Engine 2 with 100% writes using eight and sixteen threads.                                                                                                                                                         | 36       |

| 5.1 | The RNVMe command is to support calling a function on the NVMe device with multiple parameters. These parameters can either be DMA buffers or                                                                                                                                                                                      |          |

|     | 64-bit numbers                                                                                                                                                                                                                                                                                                                     | 44       |

# **List of Abbreviations**

AMD-Vi AMD's I/O Virtualization Technology

ASIC Application-Specific Integrated Circuit

AppNVM Application NVMe

BAR (PCIe) Base Address Register

CQ Completion Queue

DFC Dragon Fire Card

DMA Direct Memory Access

DPDK Data Plane Development Kit

ECC Error-correcting code

FPGA Field-Programmable Gate Array

FTL Flash Translation Layer

Intel VT-d Intel's Virtualization Technology for Directed I/O

LBA Logical Block Address

LUN Logical Unit

MLC Multi-Level Cell (NAND flash)

MTRR Memory Type Range Register

NDP Near-Data Processing NVM Non-Volatile Memory

NVMe NVM Express

NVMf NVMe Over Fabrics

OC-NVMe Open-Channel SSD NVMe

OOB Out-Of-Band

PCB Printed Circuit Board

PCIe Peripheral Component Interconnect Express

PPA Physical Page Address

PRP Physical Region Page

RPC Remote Procedure Call

SAS Serial Attached SCSI

SATA Serial ATA

SCSI Small Computer System Interface SPDK Storage Performance Development Kit

SQ Submission Queue

SSD Solid State Disk

SoC System on a Chip

UIO User-space I/O

VFIO Virtual Function I/O

XFI (10 Gigabit Small) Form Factor Pluggable

uFLIP Understanding Flash I/O Patterns

# Chapter 1

# Introduction

Data-driven application developers have been facing new challenges with today's revolutionary changes in storage technologies and the growing need for a storage of vast quantities of data. Traditionally, three separate layers have been responsible for storage access scheduling. The application, the operating system, and the on-storage controller of the storage device. Data-driven applications are designed to predict ahead of time their extensive access patterns with carefully designed execution planners. Operating systems and storage controllers, on the other hand, lack such foresight and are designed to deal with general access patterns and to make ephemeral plans. With the robust performance of new storage technologies, it has become apparent to data-driven application developers that these shortsighted schedulers have both become a bottleneck and have started to counteract the applications execution planners. Traditional database systems have been dealing with such issues for decades but what has changed in recent years is the sophistication of the devices and their storage controllers.

The most prevalent storage technology is the Solid State Disk (SSD) which has been phasing out the traditional spinning magnetic disks that dominated the market for decades. SSDs have introduced orders of magnitude better performance and have virtually eradicated the penalty of random access patterns. Despite these salient features, it has proven to be hard for data application developers to optimize for the SSDs, due mostly to the apparent differences in both physical characteristics and on-device scheduler implementations. These differences vary wildly between both vendors and SSDs models and therefore no common optimization techniques have been established. The significant shift from the previous technology is not only due to the SSD having more complex storage logic and more advanced capabilities, but also in the fact that the advancement in cheap chipset technologies has allowed the enterprise SSDs themselves to take on the characteristics of a fully functional computer.

Various solutions to these performance bottleneck problems have been explored [1], such as eliminating operating system overhead by bypassing the operating system kernel and communicating directly with the SSD from the application [2] [3]. Another solution was to expose the internal characteristics of the SSD by creating a new type of SSD called Open-Channel SSD [2] [4]. This new SSD allowed the application developer to directly control the on-device scheduling, effectively making the application's execution planner able to optimize fully down to the device level.

In our research, we have explored two avenues of optimizing the I/O access. First, we implemented and evaluated bypassing the operating system, allowing a user-space application to directly access the storage device or device controller via the Open-Channel SSD standard. Second, we propose a new way of doing near data processing (NDP) by moving part of the application logic to the storage medium.

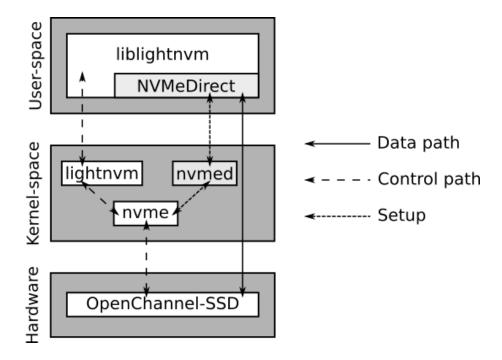

Figure 1.1: Overview of the communication pathway of the I/O traffic from user-space applications down to the storage device(s). In figure (a) we see the standard I/O traffic passing through the operating system's API. In (b) we see how the Kernel can be bypassed to reduce overhead. Finally, in (c) we depict how we can delegate part of the application logic to the storage device for near data processing.

The three parts of Figure 1.1 present an overview of the topics addressed in this thesis. The traditional enterprise SSDs use the NVMe communication protocol which exposes the SSD as a block device and conceals its physical characteristics, where it is the vendors' responsibility to make sure that the flash chips wear evenly and to utilize the internal parallelism of the SSDs according to their access pattern scheduler.

In our work, we used an Open-Channel SSD which extends the NVMe standard and exposes the internal characteristics of the device and moves the burden of wear leveling and access pattern scheduling to either the operating system or the application. Figure 1.1a shows the traditional way of communicating with an SSD where all communication from the application goes through the operating system kernel. Our contributions in this thesis as follows: First is the LightNVM-Direct, a kernel bypass for open-channel SSD. We also wrote a debugging framework to make this work easier. The second contribution is the AppNVM is a remote procedure call (RPC) system that will allow near data processing (NDP) to be done on the storage device.

The rest of this thesis is structured as follows: In Chapter 2 we cover the background material that we build our work upon, such as the storage technology (SSD), the communication protocols (NVMe) and our evaluation tools. This is followed by a short description of the debugging framework we developed in Chapter 3. In Chapter 4 we describe our first major contribution, the LightNVM-Direct bypass of the Kernel. In Chapter 5 we define our second contribution, the AppNVM. AppNVM is a remote procedure call (RPC) system that will allow near data processing (NDP) to be done on the storage device. Finally we end this thesis by drawing conclusions in Chapter 6.

# Chapter 2

# **Background**

In this chapter, we will go through the background needed for our contributions of bypassing the kernel for Open-Channel SSD based NVMe devices, and for our proposal of a new NVMe based protocol to minimize data movement by moving part of the application logic to the NVMe device. We have structured our background into four different parts.

- 1. NVMe: We start with the NVMe protocol, the main SSD protocol used today. NVMe is designed to incorporate the high parallelism that SSDs are capable of, as well as their high throughput, and thus, NVMe resides directly on the CPU's main bus for maximum performance.

- 2. User-space NVMe: After introducing the internals of NVMe, we examine what is needed to communicate with an NVMe device directly from a user-space application. We also review the limitations of bypassing the operating system kernel, and the solutions that already exist to provide a bypass for NVMe devices.

- 3. SSD: Next we review the internals of the SSD, highlighting the challenges imposed on storage developers and how Open-Channel SSD was designed to help deal with those challenges. We describe the Dragon Fire Card (DFC), a fully programmable NVMe device that we used for our implementation of the kernel bypass and our benchmark experiments, as well as its companion firmware OX, the first open source Open-Channel SSD firmware, which we ran on the DFC NVMe.

- 4. Benchmarking: Lastly we introduce the uFLIP-OC benchmark which is a benchmark for to identify the I/O patterns best suited for a given Open-Channel SSD. In our work we used a tool called *fox* which is capable of implementing the uFLIP-OC benchmark to evaluate our results. We compared our implementation to the traditional one by compiling two versions of the *fox* program, one using our kernel bypass, and another using the traditional backend. We ran the same benchmark on both of versions of *fox* and to evaluate our results.

# 2.1 Non-Volatile Memory Express (NVMe)

The NVMe communication protocol is the main SSD protocol used today. It was designed to replace the traditional spinning disks protocols SATA and SAS. Unlike the previous protocols, the NVMe protocol communicates directly through the Peripheral Component Interconnect Express (PCIe) bus, which is a high-speed serial computer expansion bus standard used to communicate with devices attached to the host computer.

From a system programmer's perspective, the programmer can read and write directly to the PCIe device registers using regular memory addresses. This memory representation is made possible by the I/O memory management unit (IOMMU) which is responsible for mapping the PCIe device registers to physical memory addresses. The PCIe registers of a device mapped to physical memory are together called the PCI Configuration Space. This configuration space is standardized to make it easy for Operating Systems to identify the device and for drivers to find their driver specific registers, called the Base Address Registers (BARs). Each BAR points to a region of device-specific registers which represent the main interface to the device's functionality used by driver programmers.

For our contribution, we only need to focus on the most relevant BAR register. The NVMe standard defines a mandatory memory layout, pointed to by the main BAR that all NVMe devices must implement. This layout contains special registers that manage queues that are used to send administration and I/O commands.

#### 2.1.1 DMA memory

Direct Memory Access (DMA) is a mechanism to offload work from the CPU by allowing the device to access the physical memory of the host independently from the CPU. In modern high-speed devices, it is used to transfer data to and from the main physical memory and the device. When either the device or the CPU has prepared the data into a DMA buffer, they can notify each other that the data is ready for consumption. The CPU sends notifications by writing into a notification register on the device, while the device signals the CPU by signaling an interrupt.

## 2.1.2 NVMe queues

The NVMe standard's primary means of communicating with the NVMe device is through two queue types called submission and completion queues. The host uses the submission queue to send NVMe commands to the NVMe device, and the NVMe device uses the completion queue to notify the host of completed NVMe commands. Both of these queues are DMA buffers and are circular lists for NVMe commands, as seen in Figure 2.1.

Since the queues are a communication abstraction that does not present any physical characteristics of the device, the driver programmer can create as many queues as needed. This decision could be one queue per CPU core or one queue per thread, depending on the requirements and design. In our design, we decided to create one submission and completion queue per pthread.

#### 2.1.2.1 Admin queue

The admin queue is a particular queue which is only used to send administrative commands to the NVMe device and is the only queue that is always available. This queue is identical to every other queue, apart from having the lowest identity number, zero.

One of the primary functions of the admin queue is to create a new submission and completion queues. These queues are created by submitting the create submission queue and the create completion queue commands. Table 2.1 lists most of the standard administration commands and Figure 2.2 shows the communication flow through those queues.

Figure 2.1: NVMe queues are DMA buffers used by the host to submit commands to the NVMe device. The queues are circular buffers, where the submission queue is used by the host to submit commands, and the completion queue is used to notify the host of completed commands. The host keeps track of the tail pointer of the submission queue, and the NVMe device keeps track of the head pointer of the completion queue.

Figure 2.2: NVMe devices have one admin queue which the host uses to create submission and completion queues. The queues are DMA memory buffers which the host uses to send I/O commands to the NVMe device. This Figure is based on a Figure by Picoli [5]

# 2.1.3 The queue structure and notification doorbells

The submission and completion queues are made up of two distinct parts: the DMA buffer and its associated register in the NVMe BAR. Table 2.2 shows the two registers, the submission queue tail doorbell, and the completion queue head doorbell, which are owned by each queue in the BAR. These doorbells are used to notify the SSD when the host has either inserted new entries into the submission queue DMA buffer or processed one or more completion entries from the completion queue DMA buffer. The host notifies the NVMe device about changes by writing the location of the head and tail pointers to their respective registers as seen in Figure 2.1.

| Opcode | Command                     |

|--------|-----------------------------|

| ooh    | Delete I/O Submission Queue |

| 01h    | Create I/O Submission Queue |

| o4h    | Delete I/O Completion Queue |

| o5h    | Create I/O Completion Queue |

| o6h    | Identify                    |

| 09h    | Set Feature                 |

| oAh    | Get Feature                 |

|        |                             |

Table 2.1: This table lists the most common NVMe admin commands. It is only possible to send these commands to the admin queue.

The SSD shares the DMA queues with the host when the host sends the size and the physical address pointer to the queues using the create submission queue and create completion queue commands. These commands make sure that both the host and the NVMe device agree on the DMA buffers.

#### 2.1.4 NVMe commands

The NVMe standard defines 64-byte command entries for the submission queue and 16-byte completion queue entries. The standard further breaks down those bytes into 16-bit words; however, most written work and code refers to double words or DW for short.

Figure 2.3 shows the structure of a typical NVMe submission command. All commands share the same format for the first two DW. The opcode field tells the NVMe device which command is being submitted and in turn what fields to expect in DW four to thirteen. Table 2.3 lists the three most common NVMe commands.

The completion entries are 16-bytes or four DW and contain five fields, as shown in Figure 2.4. The status field holds both the return value of a completed command and a phase bit. This phase bit is used to tell the driver if the completed command is an old command from the last circulation, and is flipped by the NVMe device every time it needs to move the head pointer to the beginning of the circular DMA buffer.

# 2.2 User-Space NVMe

A popular method to improve the performance of high-speed devices has been to bypass the kernel and write directly to the device from user-space, as was depicted in Figure 1.1b. This method starts to become beneficial when the round-trip time of an NVMe command is less than a context switch quantum. Bypassing the kernel was first studied on network devices when their throughput exceeded the capacity of the CPU and has now been explored by researchers on SSDs for the same reasons. An excellent example of this is the NVMeDirect library developed by Kim, Lee, and Kim, which we decided to base our bypass on, and the open source solutions developed outside of academia, such as Intel's SPDK [4] [6] and Micron's unvme [7].

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Start                       | End                         | Symbol   | Description                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|----------|------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00h                         | 07h                         | CAP      | Controller Capabilities      |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 08h                         | OBh                         | VS       | Version                      |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0Ch                         | OFh                         | INTMS    | Interrupt Mask Set           |

| 18h       1Bh       Reserved       Reserved       Reserved         1Ch       1Fh       CSTS       Controller Status         20h       23h       NSSR       NVM Subsystem Reset (Optional)         24h       27h       AQA       Admin Queue Attributes         28h       2Fh       ASQ       Admin Submission Queue         30h       37h       ACQ       Admin Completion Queue         Base Address       Optional and reserved fields         1000h       1003h       SQoTDBL       Submission Queue o Tail Doorbell (Admin)         1000h + 1·       (4 << CAP.DSTRD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10h                         | 13h                         | INTMC    | Interrupt Mask Clear         |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14h                         | 17h                         | CC       | Controller Configuration     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18h                         | 1Bh                         | Reserved | Reserved                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1Ch                         | 1Fh                         | CSTS     | Controller Status            |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20h                         | 23h                         | NSSR     |                              |

| 30h 37h ACQ Admin Completion Queue Base Address Optional and reserved fields 1000h 1003h SQoTDBL Submission Queue o Tail Doorbell (Admin)  1000h + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24h                         | 27h                         | AQA      | Admin Queue Attributes       |